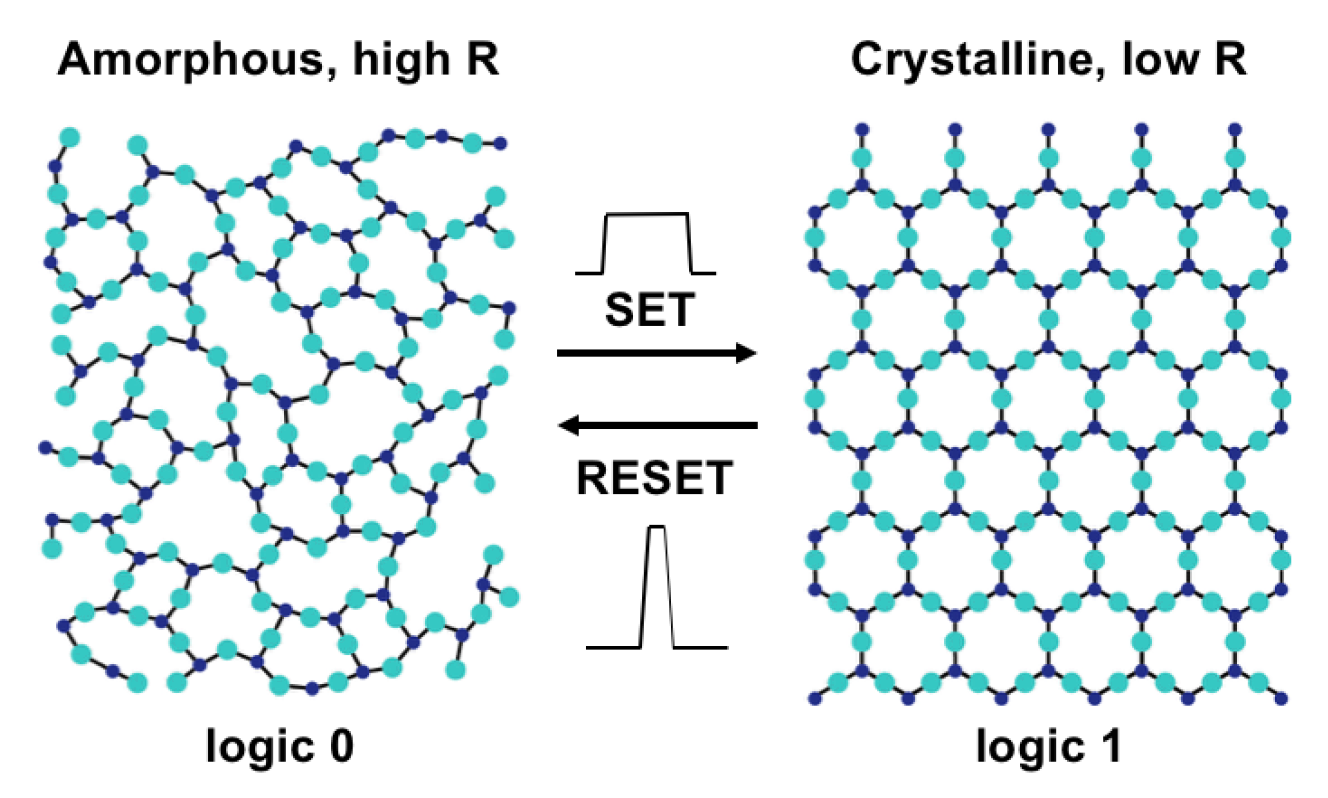

GST is the phase change material commonly used in phase change memory (PCM). It has a high-resistance amorphous phase and a low-resistance crystalline phase.

.

.

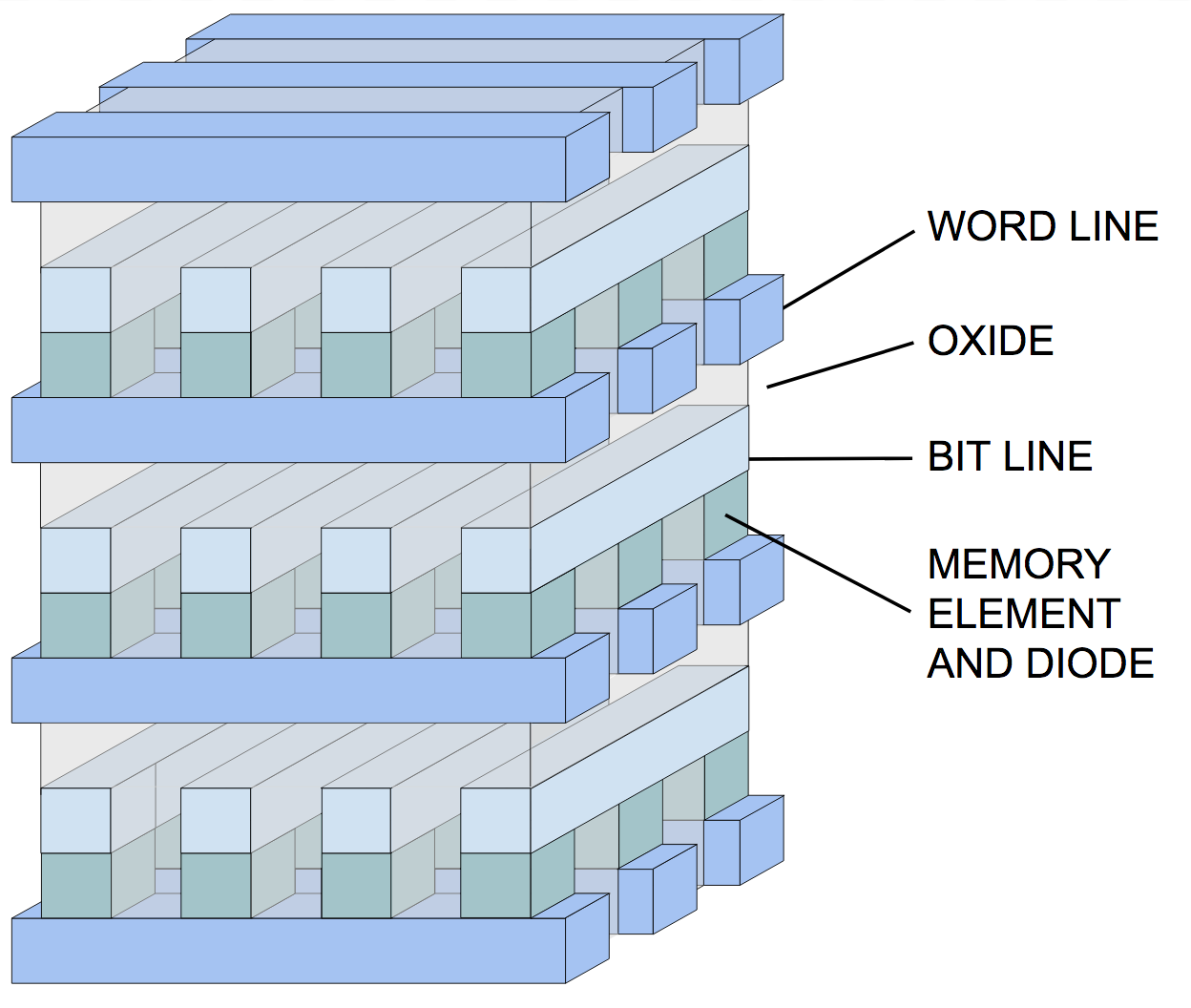

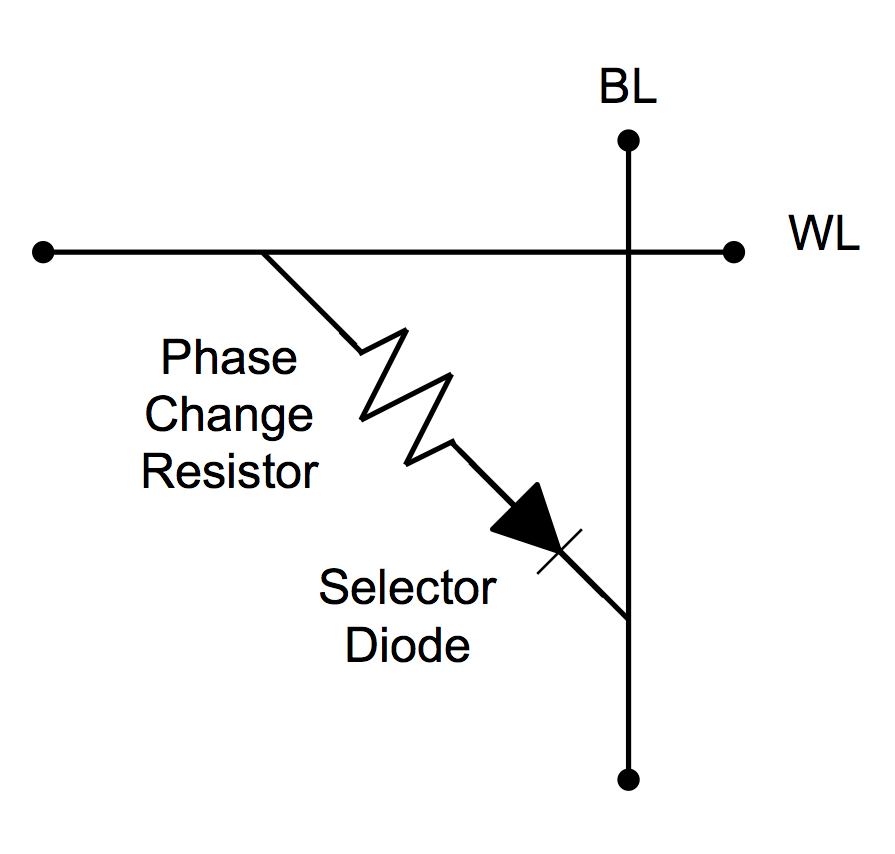

In addition to being low power and low cost, phase change memory can be used in a cross point architecture, allowing for increased density and scalability.

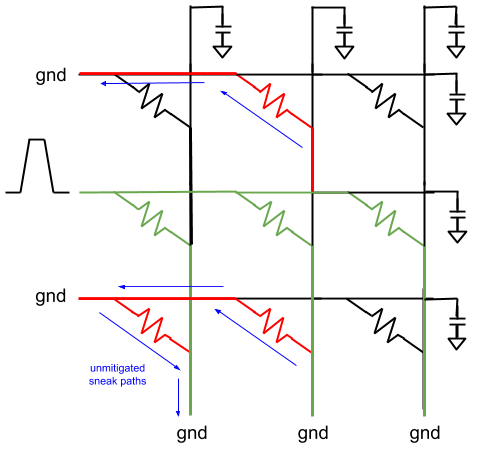

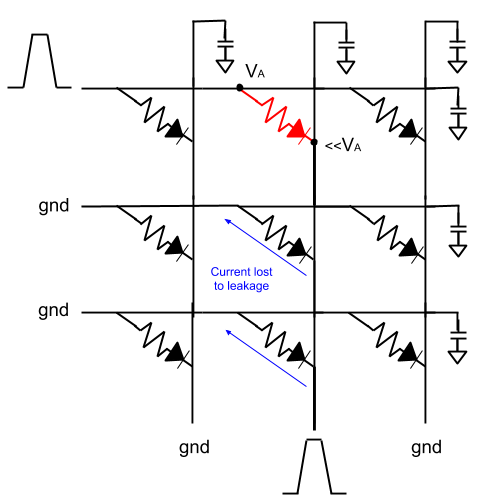

During the non-ideal operation of a 1R cross-point PCM array, current may flow through non-target cells if there is a path of lower resistance.

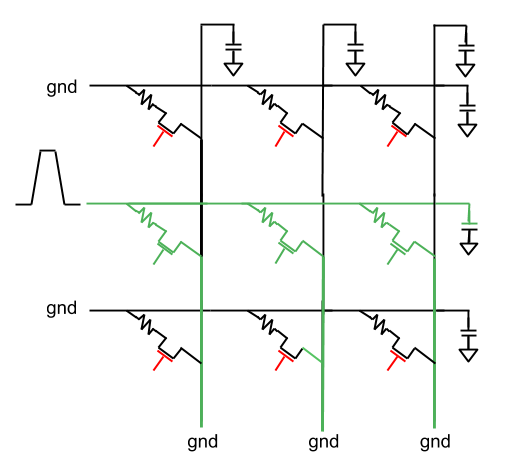

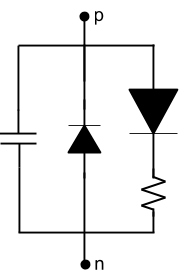

Selectors, which can be either transistors or diodes, can mitigate these sneak paths by limiting where current can flow. 1D1R PCM, which uses diodes as selectors, offers further increased density compared to its 1T1R counterpart, which is already commercially available. However, diodes leak some current in reverse bias and this leakage may limit bitline swing.

The ultimate goal of the simulation framework is thus to quantify the effects of diode leakage on maximum array size and determine the quality of diodes necessary for ideal performance.

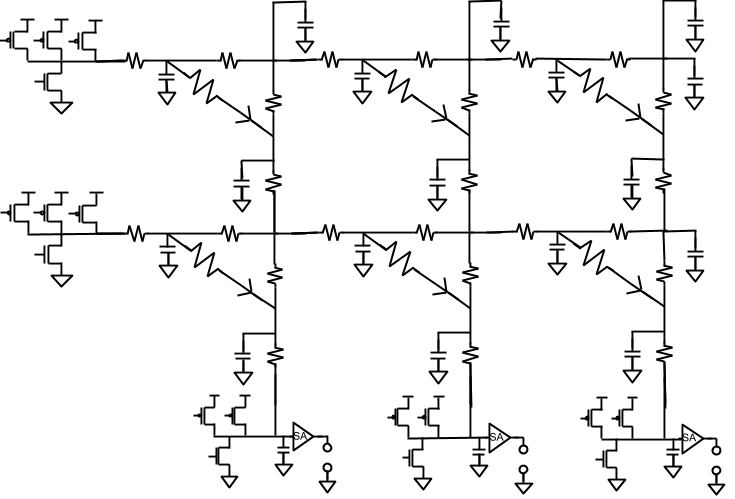

We used Verilog-A to model the hardware of the PCM device and selector diode, and HSPICE to describe the netlist of the full array model for simulation. The resulting full array model includes drivers, PCM devices, selector diodes, and wire parasitics.

Though the full array model matches actual behavior closely, large arrays take days to run or fail altogether. We instead used a simple cell model which replaces the PCM device of each non-target cell with a simple resistor to decrease runtime. This relies on the underlying assumption that the resistance in other cells remain constant.

Acknowledgements: Carla Becker, Hamzah Khan, Josephine King, Matthew Spencer